So they found a way to inscribe more arcane runes onto the mystic rock thus increasing its mana capacity?

That’s pretty much it yeah

Can’t wait for Python on top of webassembly on top of react on top of electron Frameworks to void that advancement

This is the best summary I could come up with:

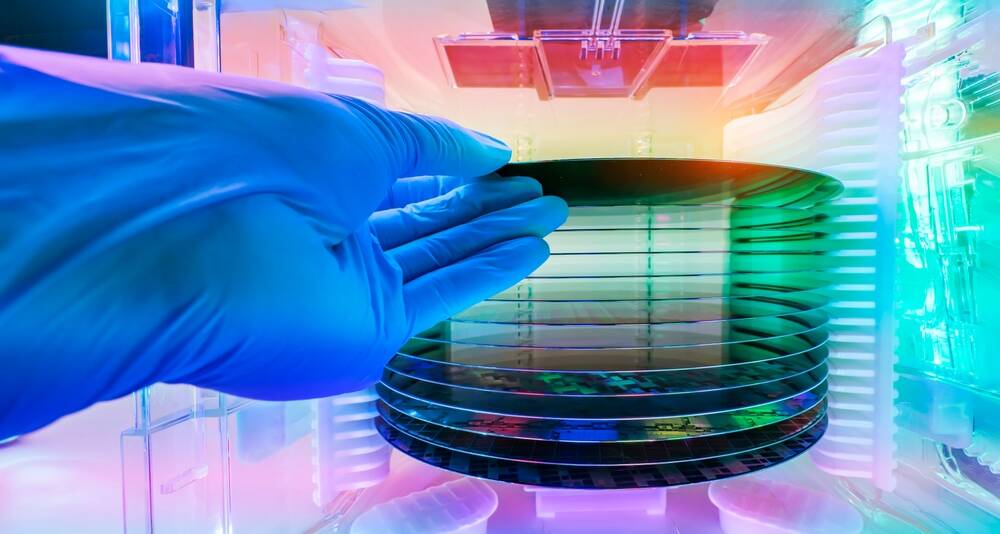

TSMC disclosed that A16 will combine its nanosheet transistor design, set to be introduced on 2nm, with Super Power Rail technology.

According to Reuters, TSMC indicated that it does not need ASML’s latest High NA EUV photolithography machines in order to produce chips with its A16 process.

This adds area-efficient design rules that are compatible with its popular N4P process, but which will deliver an 8.5 percent die cost reduction for “value-tier” products, TSMC claims.

This enables a large array of dies on a 300 mm wafer to form a single system, boosting compute power while occupying far less space.

TSMC also said it is developing Compact Universal Photonic Engine (COUPE) technology for high-speed interconnects, citing AI as an application that will need this.

TSMC reported revenue up year-on-year for the first quarter of 2024 earlier this month, beating expectations, and said it anticipated that demand for AI-capable PCs and datacenter kit will drive higher sales of the silicon it produces this year.

The original article contains 686 words, the summary contains 163 words. Saved 76%. I’m a bot and I’m open source!

Aren’t these sizes a marketing gimmick anyway? They used to mean the gate size of a transistor, but I don’t think that’s been the case for a few years now.

They’re generally consistent within a single manufacturer’s product lines; however, you absolutely cannot compare them between manufacturers because the definitions are completely different.

I think I’m just skipping the whole 20,30,40 series as well as the 7nm series…my 9900k and 1080ti are doing me just fine. Maybe 2026 I’ll consider upgrading.

What’s the threshold for quantum tunneling to be an issue? Cuz at such small scales, particles can…teleport through stuff.

Quantum tunneling has been an ongoing issue. Basically, they are using different design of transistors, different semiconductor material at the gate, and accepting that it is a reality and adding more error checks/corrections.

It’s important to note that 1.6nm is just a marketing naming scheme and has nothing to do with the actual size of the transistors.

https://en.m.wikipedia.org/wiki/3_nm_process

Look at the 3nm process and how the gate pitch is 48nm and the metal pitch is 24nm. The names of the processes stopped having to do with the size of the transistors a couple of decades ago. It is stupid.

That is ridiculous. Does 3nm mean anything or it is purely marketing?

Every process name is basically a marketing a gimmick. You could sort of use the previous names as a ratio to get a general idea of uplift but that isn’t really accurate either. To further confuse things Intel’s naming scheme had bigger nm values but is a similar size to lower numbered names from TSMC.